<sup>#</sup> Prof. N. V. Uma Reddy, Research Scholar, VTU, Bangalore, India. nvumareddy@gmail.com

\* Dr M V Chaitanya Kumar, Principal & Professor, KNSIT, Bangalore, India. chaitanya126@yahoo.com

Abstract— 4-bit high speed R-2R Ladder Digital to Analog Converter (DAC) design is presented in this paper. The high speed DAC design uses a high speed InGaAs/GaAs HEMT device in its summer block. This paper justifies the use of HEMT devices for high speed converter applications. A detailed analysis of the DAC parameters and errors is presented. DAC performance up to 20GHz is presented and it shows very good DNL and INL performance, and stable offset and resolution over the frequency range up to 20 GHz.

Index terms - DAC, DNL HEMT, INL, Linearity, Resolution, R-2R ladder, V<sub>LSB.</sub>

#### I. INTRODUCTION

HE rapid developments in Radio Frequency (RF) L technologies like satellite communication, broadband communication and monolithic microwave integrated circuit (MMIC) have encouraged researchers to develop new high frequency devices described by low noise figures and higher cut-off frequencies. Our research work presented in [1] introduces one such high electron mobility transistor (HEMT) device characterized by its low noise and high frequency operations. The advantages of HEMTS in RF circuits is highlighted by researchers [2], [3], [4], [5]". The dominance of high frequency digital circuits in the RF arena is well established [6]. In order to process digital data for high speed RF digital circuits the analog signals need to be digitally represented and vice versa hence Analog to Digital Convertors (ADC) / DAC's provide an interface to achieve this. The accuracy of digital representation and performance at such high frequencies are critical to the overall system. Hence this paper represents a high frequency DAC using the hetrojunction HEMT presented in [1].

Researchers have used HEMTS to create high frequency RF applications like oscillators [7], [8], [9], [10], programmable decimators [11], optical applications [12], ADC's [13], [14], [15] and high frequency switching applications [16] has been closely studied during the course of the research presented here. There are limited or rare use of HEMTs to realize DACs which was another motivating factor for the authors[17], [18].

This paper is arranged as follows. Section II describes the Digital to Analog Converters and different performance parameters that determine the DAC performance. In Section III, the R-2R ladder DAC implementation is presented and a detailed calculation of the DAC parameters done. Section IV discusses the simulation results which are concluded in Section V.

#### **DIGITAL TO ANALOG CONVERTERS** II.

Digital to Analog Converters (DACs) are an important element of any mixed signal circuit [19]. They are necessary to interface the digital world of the processors with the physical world which recognizes and appreciates signals in the analog domain (sound, light, etc). A DAC converts a digital signal into an equivalent analog signal.

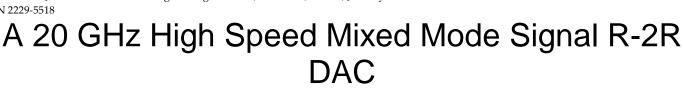

In this paper R-2R DAC is considered. The architecture is as given in Fig. 1 and the Equation 1 defines the output voltage of the DAC for different bit patterns.

$$V_{out} = I.R_f = V_{ref} \left( B_3 + \frac{B_2}{2} + \frac{B_1}{4} + \frac{B_0}{8} \right) \qquad \dots (1)$$

Figure 1: R-2R Ladder DAC

The performance of a DAC is evaluated by certain parameters as described in the following:

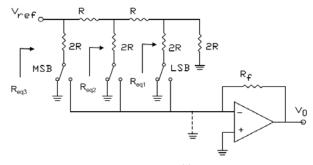

1. Resolution: It is defined as the amount of variation in the output voltage for every change of the LSB in the digital input. It is a measure of how clearly can we approximate the desired output signal. For an N-bit DAC with reference voltage as V<sub>ref</sub>, resolution is computed by Equation 2 and in Fig. 2

$$Resolution = V_{LSB} = \frac{V_{ref}}{2^N} \qquad \dots (2)$$

- 2. <u>Reference Voltage</u>: It is defined as a specified voltage used to determine how each digital input will be assigned to each voltage division.

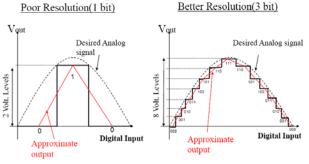

- 3. <u>Settling Time</u>: It is the time required for the input signal to settle within  $\pm V_{LSB}$  of the expected output voltage. The concept of settling time is shown in Fig. 3.

Figure 2: Resolution of a DAC

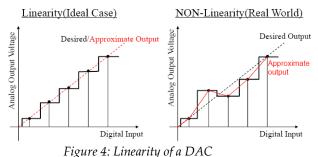

4. <u>Linearity</u>: It is the difference between the desired analog output and the actual output over the full range of expected values as shown in Fig. 4.

5. <u>Speed</u>: It is the rate of conversion of a single digital input to its analog equivalent and depends on the clock speed of the input signal as well as the settling time of the converter.

The performance evaluation of DAC [20] is also done by the different types of errors as described next:

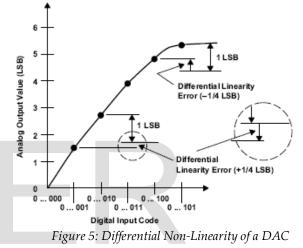

- 1. <u>Differential Non-Linearity (DNL)</u>: DNL is the difference between an actual step height and the ideal value of 1LSB. Hence if the step height of a DAC is equal to 1LSB, then DNL is zero. If DNL is more than 1 LSB, then the converter can become no-monotonic as in Fig. 5.

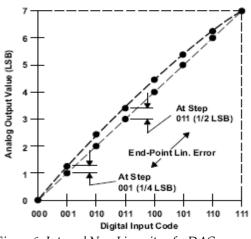

- 2. <u>Integral Non-Linearity (INL)</u>: INL is the deviation of the values on the actual transfer function from a best fit straight line as in Fig. 6.

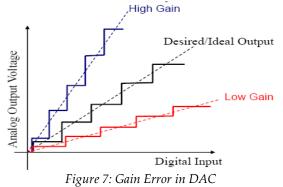

- 3. <u>Gain Error</u>: It is the difference between the slope of the ideal curve and the actual DAC output as shown in Fig. 7

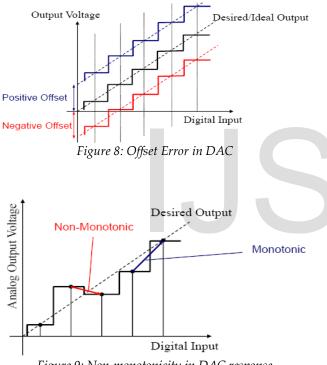

- 4. <u>Offset Error</u>: It is the constant voltage difference between the ideal DAC output and the actual output as in Fig. 8.

Figure 6: Integral Non-Linearity of a DAC

5. <u>Non-Monotonicity</u>: It is the decrease in the output voltage with an increase in the digital input as in Fig. 9.

*Figure 9: Non-monotonicity in DAC response*

# III. R-2R LADDER DAC IMPLEMENTATION

# A. Circuit Simulation in Spice:

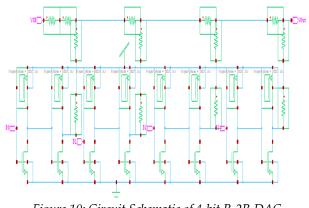

An R-2R ladder DAC is simulated in Spice Simulator with InGaAs/GaAs HEMT transistor based summer. The design and results of the high speed HEMT transistor were reported in [1]. The circuit schematic for a 4-bit DAC is shown in Figure 10.

Figure 10: Circuit Schematic of 4-bit R-2R DAC

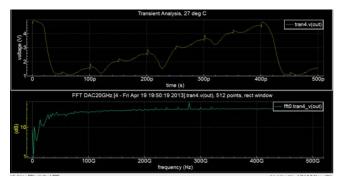

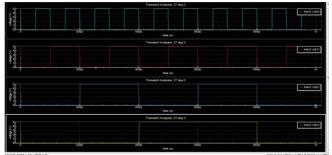

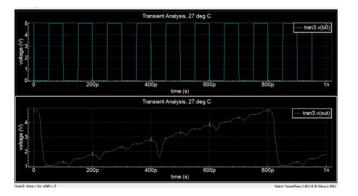

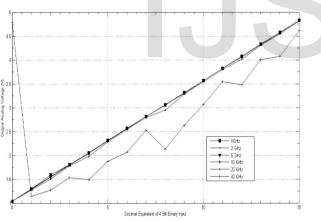

The circuit is simulated using a Spice simulator for all the ranges of 4-bit input patterns ( $0000_2$ -1111<sub>2</sub>). The simulation inputs as given in Fig. 11 and 13 are provided in the form of 4 pulse trains representing b<sub>3</sub>-b<sub>0</sub> (MSB-LSB). The frequency of the pulse representing b<sub>0</sub> determines the operating frequency of the DAC. The circuit simulation results are presented for a frequency range from 20GHz to 40GHz as shown in Fig. 12 and 14. A linear fit of the output voltage is done for calculating various parameters as described in the next section III B .

Figure 11: Simulation inputs for 20GHz

Figure 12: Analog Output of DAC at 20GHz

Figure 13: Simulation inputs for 40GHz

Figure 14: Analog Output of DAC at 40GHz (curve in red is the straight line fit)

Figure 15: DAC Analog Output for all frequencies

## **B. DAC Parameter Calculations:**

- 1. <u>Offset, V<sub>off</sub></u>: Offset Voltage for the design is 1.039V except at 40GHz.

- 2. <u>Resolution</u>: V<sub>ref</sub> for the implemented R-2R ladder DAC is 5V. Hence the ideal resolution is given by Equation 4. However, from simulation results it is seen that the DAC offset is 1.039V. Hence the actual resolution of the DAC is given by equation 5 and it can be seen that the resolution

is different for different frequencies as tabulated in Table 1.

Resolution =

$$V_{LSB}$$

$$=\frac{5V}{2^4} = 0.3125V \qquad \dots (4)$$

$$\begin{aligned} \text{Resolution} &= V_{\text{LSB}} \\ &= \frac{V_{\text{out,max}} - V_{\text{out,min}}}{2^{N}} \end{aligned} \qquad \dots (5)$$

$$V_{LSB}at \ 1GHz = \frac{4.83 - 1.039}{2^4} = 0.237V \qquad \dots (6)$$

3. <u>Linearity</u>: Based on the results shown in Figure 30, the nonlinearity of the DAC at different frequencies is calculated as in Equation 7 and the results are tabulated in Table 1.

$$Linearity = \frac{\Delta V}{Output Range} \qquad \dots (7)$$

4. <u>Differential Non-Linearity</u>: DNL is analytically calculated using Equation 8. Calculations are shown for 1GHz frequency and the results for other frequencies are compiled in Table 1.

$$DNL = \max\{V_{out}(i + 1) - V_{out}(i) - V_{LSB}\}$$

$$= 1.594-1.295-0.237$$

$$= 0.26 V_{LSB}$$

...(8)

<u>Integral Non-Linearity</u>: INL is computed by using Equation 9. Here, V<sub>out</sub>(code) is the output voltage at a given binary code and V<sub>ft</sub>(code) is the output at the same code for a linear fit curve. The calculations for 1GHz are shown in Equation 9. Other results are compiled in Table 1.

$$INL = \max\{V_{out}(code) - V_{fit}(code)\}$$

/ $V_{LSB}$  ...(9)

= (1.594-1.56)/0.237

$= 0.14 \text{ V}_{\text{LSB}}$

6. <u>Monotonicity</u>: Figure 15 shows that the DAC response is monotonically increasing for all frequencies 1 GHz to 20 GHz except at 40GHz. At 40GHz, the DAC, DNL is negative at input values of 0100<sub>2</sub>, 1000<sub>2</sub> and 1100<sub>2</sub>. Hence, the DAC cannot be used at 40GHz operating frequency.

### IV. RESULTS AND DISCUSSION

This section summarizes the results computed in Section III.B.

| Table 1<br>DAC parameters at different operating frequencies |                         |             |                  |              |              |

|--------------------------------------------------------------|-------------------------|-------------|------------------|--------------|--------------|

| Freq<br>(GHz)                                                | V <sub>off</sub><br>(V) | VLSB<br>(V) | Linearity<br>(%) | DNL<br>(LSB) | INL<br>(LSB) |

| 20                                                           | 1.039                   | 0.236       | 2.11             | 0.402        | 0.337        |

- 1. The offset voltage of DAC is a high value of 1.039. However, it is fixed over the entire frequency range under consideration which is a good performance criterion.

- 2. Resolution of the DAC over the frequency range is constant value and hence, the DAC is usable over the frequency range up to 20GHz.

- 3. Differential non-linearity and integral nonlinearity of the designed DAC are also small fraction of LSB. This shows that the DAC performance over the entire input range is good.

- 4. As the DAC response for 40GHz is nonmonotonic as in Fig. 15, the DAC cannot be used at 40GHz frequency and hence the calculations are not presented at 40GHz and the DAC is usable upto a frequency of 20GHz.

### V. CONCLUSION

A high speed R-2R ladder 4-bit DAC design using an InGaAs/GaAs HEMT and performance analysis for the same was presented. The HEMT device used was designed for high speed converter applications and was reported in earlier publications. A thorough analysis of the DAC parameters and the calculations of the errors at different operating frequencies are presented in this paper.

The DAC implemented has a unity gain summer designed using the high speed HEMT device, which is used for summing the weighted voltages due to the digital input. The simulation results are presented for 20GHz and 40GHz frequencies. The analog output follows the input fit a very good linear fit for frequencies up to 20GHz. The DAC response is monotonous up to 20GHz frequencies. The designed DAC is reported to have a worst INL DNL of 0.337LSB and 0.402LSB.

It is concluded that the design based on earlier reported HEMT device is suitable for DAC applications up to 20GHz; the DAC has demonstrated very good linearity and error performance.

#### REFERENCES

- [1] N V Uma Reddy and M V Chaitanya Kumar," InGaAs/GaAs HEMT for High Frequency Applications", International Journal of Soft Computing and Engineering (IJSCE). Volume-3, Issue-1, March 2013. pp 16-20

- [2] D. Pavlidis, "HBT vs. PHEMT vs. MESFET: What's best and why," inProc. GaAs MANTECH Conf., Vancouver, Canada, 1999.

- [3] C. Y. Chang and F. Kai, GaAs High-Speed Devices. New York: Wiley, 1994.

- [4] Y. Yamashita, A. Endoh, K. Shinohara, K. Hikosaka, T. Matsui,S. Hiyamizu, and T. Mimura, "Pseudomorphic In Al As–In Ga As HEMTs with an ultrahigh f of 562 GHz," IEEE Electron Device Lett., vol. 23, pp. 573–575, Nov. 2002.

- [5] Kartika Chandra Sahoo, Chien-I Kuo, Yiming Li,and Edward Yi Chang,"Novel Metamorphic HEMTs With Highly Doped InGaAs Source/Drain Regions for High Frequency Applications", IEEE Transactions On Electron Devices, Vol. 57, No. 10, October 2010.

- [6] Tingting Shi, Sijian Hou, Ping Luo, Ruhui Yang, Jun Chen, Shaowei Zhen, and Bo Zhang."A Low Power and High Precision DAC in 0.13 film CMOS for DVS System", Communications, Circuits and Systems (ICCCAS), 2010 International Conference. pp 585 – 588

- [7] S. Rosenbaum, B. Kormanyos, L. Jelloian, M. Matloubian, A. Brown, L. Larson, L. Nguyen, M. Thompson, L. Katehi, and G. Rebeiz, "155-and 213-GHz AlInAs/GaInAs/InP HEMT MMIC oscillators," IEEE Trans. Microw. Theory Tech., vol. 43, no. 4, pp. 927–932, Apr. 1995.

- [8] V. Radisic, L. Samoska, W. Deal,X.Mei,W. Yoshida, P. Liu, J. Uyeda, A. Fung, T. Gaier, and R. Lai, "A 330-GHzMMIC oscillator module," in IEEE MTT-S Int. Microw. Symp. Dig., Jun. 2008, pp. 395–398.

- [9] V.Radisic,X.Mei,W.Deal, W. Yoshida, P. Liu, J. Uyeda,M. Barsky, L. Samoska, A. Fung, T. Gaier, and R. Lai, "Demonstration of sub-millimeter wave

fundamental oscillators using 35-nm InP HEMT technology," IEEE Microw. Wireless Compon. Lett., vol. 17, no. 3, pp. 223–225, Mar. 2007.

- [10] J.-W. Lee, S.-W. Kim, K.-S. Seol, Y. Kwon, and K.-S. Seo,"HIGH POWER 60 GHz PUSH–PUSH OSCILLATOR USING INALAs/InGaAs METAMORPHIC HEMT TECHNOLOGY", MICROWAVE AND OPTICAL TECHNOLOGY LETTERS / Vol. 49, No. 3, March 2007. Pp 609-612

- [11] Javad Frounchi and Steve J. Harrold," Multigigabit programmable comb decimator implemented in GaAs/AlGaAs HEMT technology", Gallium Arsenide Applications Symposium. GAAS 1999, 4-5 October 1999, Bologna, Italy.

- [12] Tamotsu KIMURA, Tomoyuki OHSHIMA, Masanori TSUNOTANI, Toshihiko ICHIOKA and Shohei SEKI," GaAs pHEMT Technology for Optical Communication System", 2002 GaAsMANTECH Conference

- [13] Petros Tsenes and Nikolaos Uzunoglu," A 4-bit 7.5 GHz A/D Converter", 11th GAAS Symposium -Munich 2003

- [14] Frank Oehler, Josef Sauerer, Richard Hagelauer, Dieter Seitzer, Ulrich Nowomy, Brian RaynoP, and Joachim Schneider,"A 3.6 Gigasamplek 5 bit Analog to Digital Converter using 0.3 pm AlGaAs-HEMT Technology", Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, 1993. Technical Digest 1993.,pp 163 – 166

- [15] C.P. Lee, N.H. Sheng, H.F. Lewis, H.T. Wang, D.L. Miller and J. Donovan," GaAs/GaAlAs high electron mobility transistors for analog-to-digital converter applications", Electron Devices Meeting, 1985 International (Volume:31). pp 324 - 327

- [16] Jae-Gil Lee, Ho-Jung Lee and Ho-Young Cha,"Field Plated AlGaN/GaN-on-Si HEMTs for High Voltage Switching Applications", Journal of the Korean Physical Society, Vol. 59, No. 3, September 2011, pp. 2297-2300

- [17] Seki. S, Saito T, Fujishiro H.I, Nishi. S,and SanoY "An 8-bit 1-GHz digital to analog converter using 0.5 mu m gate inverted HEMTs", Electron Devices Meeting, 1988. IEDM '88. Technical Digest, pp 770 – 773

- [18] Rakhee Gupta ,"Analog integrated circuit design using GaAs C-HFETs", Oregon State University, 1992

Linear integrated circuits - 94 pages

- [19] Cogdell, J.R. Foundations of Electrical Engineering.2<sup>nd</sup> ed. Upper Saddle River, NJ Prentice Hall, 1996

- [20] <u>http://www.maximintegrated.com/app-notes/index.mvp/id/283</u> INL/DNL Measurements of high speed converters.

Mrs. Umareddy N. V. received her BE (Electronics) degree from Kuvempu University in 1995 and M. Tech (Electronics) degree from Viveswaraya technological University Belgaum, India in 2004, presently pursuing PhD in VTU, Bangalore, India. She has more than fifteen years of experience in teaching, her area of interest include CMOS VLSI, HDL, CCN, AMS. Presently she is the Head of the Department, Department of Electronics and Communication Engineering, AMC Engineering College, Bangalore.

Dr. CHAITANYA KUMAR M V, Ph.D., FIETE, MIOE, received his BE (Electronics) degree from University Visweswariah College of Engg INDIA in 1983, and ME (Microwave & Radar Engg) degree from the University of Roorkee, Roorkee, India (now IIT-R) in 1991 and the Ph.D. degree on (Electronics & Computer Engg.) from the University of Roorkee, Roorkee, India in 1994. He has more than 29 years of experience in Teaching, 20 years of Administrative Experience and 6 years of Research Experience. He has been a Member of the Academic Senate VTU, Belgaum during the year 2007 - 10, He is now the Principal and Professor in KNSIT, Bangalore. His areas of interests include Electromagnetic wave Absorbers, Microwave and Radar technology.